## InP/InGaAs SHBTs with 75 nm collector and $f_T > 500 \text{ GHz}$

W. Hafez, Jie-Wei Lai and M. Feng

InP/InGaAs single heterojunction bipolar transistors (SHBTs) are fabricated exhibiting current-gain cutoff frequencies,  $f_T$  of 509 GHz. The  $0.35 \times 12 \ \mu \text{m}^2$  devices consist of a 25 nm graded base and a 75 nm collector, have a breakdown  $BV_{CEO}$  of 2.7 V, and operate at current densities above 1100 kA/cm². This work demonstrates clear progress toward a THz transistor.

Introduction: Efforts to improve  $f_T$  are focusing on the reduction of electron transit time by vertically scaling the base and collector thicknesses at the cost of increasing base-collector parasitic capacitance [1–6]. An estimated 75% of the total delay time comes from the electron transit time, therefore, transit time reduction is a very efficient way to boost device speed through vertical scaling. It is well understood that the improvement in  $f_T$  from vertical scaling comes at the expense of a reduction in  $f_{\text{MAX}}$  and breakdown voltage. To compensate the drop in  $f_{\text{MAX}}$ , lateral scaling of the device dimensions must be employed to facilitate transistors with sufficiently high speeds to be useful in circuit applications. This Letter demonstrates vertically and laterally scaled HBT devices achieving state-of-the-art performance of  $f_T$  = 509 GHz, the fastest bipolar transistor reported to date.

Device layer structure and fabrication: The layer structure used in the fabrication of these devices is a scaled extension of the structure detailed in [2]. The epitaxial structure consists of a 300 nm subcollector Si doped at  $n=4\times10^{19}\,\mathrm{cm}^{-3}$ , a 75 nm collector doped at  $n=1\times10^{16}\,\mathrm{cm}^{-3}$ , a 25 nm compositionally graded base (0.53 to 0.50 Indium grading) Carbon doped to  $p=6\times10^{19}\,\mathrm{cm}^{-3}$ , and a 40 nm emitter cap with a doping of  $n=4\times10^{19}\,\mathrm{cm}^{-3}$ . The base sheet resistance is measured to be 1030  $\Omega/\mathrm{square}$ , as determined from TLM measurements.

Fabrication follows a standard triple mesa, all wet-etch process previously detailed in [7, 8]. The primary reason for the achievement of simultaneously high  $f_T$  and  $f_{\rm MAX}$  values in these devices is attributed to the use of a metal bridge, referred to as a  $\mu$ -bridge, which is undercut to eliminate the parasitic base to collector capacitance associated with the large base contact post. The process flow includes e-beam defined Ti/Pt/Au emitter contacts, a self-aligned emitter etch, a self-aligned Ti/Pt/Au base metal deposition, a base–collector etch, and collector metal deposition. A bisbenzocyclobutene (BCB) based etch-back process is employed for device planarisation and back end fabrication.

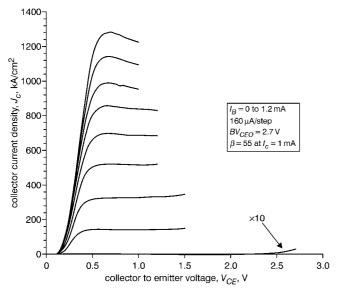

Fig. 1 Common collector output characteristics for  $0.35 \times 12 \ \mu m^2$  device

Device results: Fig. 1 shows common-emitter output characteristics for a  $0.35 \times 12 \, \mu\text{m}^2$  HBT. The current gain,  $\beta$ , for the devices varies with collector current; values range from 50 at  $I_C = 0.5$  mA to 68 at  $I_C = 25$  mA. Junction ideality factors are 1.34 and 1.14 for the base

and collector, respectively. The breakdown for this device is measured at approximately  $BV_{CEO} = 2.7 \text{ V}$  as shown in Fig. 1. This breakdown value, however, can be misleading, as the breakdown under operating conditions is much lower. It is important to note the presence of thermal effects around the peak  $f_T$  operating current of this device ( $I_C = 47.2 \text{ mA}$ ,  $V_{BE} = 0.94 \text{ V}$ ); thermal pulldown and gain compression at high current levels are, along with Kirk effect, the dominant mechanisms limiting the bandwidth of the devices.

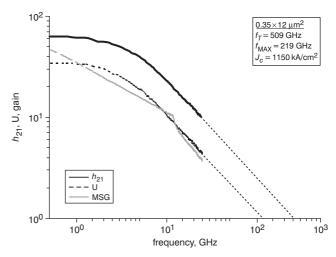

The RF calibration was achieved using an on-wafer short-open-load-thru (SOLT) calibration, and *S*-parameters were obtained using an HP8510C from 50 MHz to 50 GHz. On-wafer calibration is preferred, as it requires no additional deembedding of dummy structures, which can create a significant source of error when removing parasitic pad capacitances that approach the same order of magnitude as device capacitances. The extrapolations were obtained by assuming a  $-20~{\rm dB/decade}$  slope from the  $h_{21}$  and U curves, as shown in Fig. 2 for a  $0.35\times12~{\rm \mu m}^2$  device. The extrapolated  $f_T$  and  $f_{\rm MAX}$  values remained independent of extraction frequency out to 50 GHz, indicating that a good calibration was achieved. All RF measurements were carried out at a collector/base voltage  $V_{CB}=0$  V, which was shown to yield the highest  $f_T$  performance.

Fig. 2  $h_{2I}$ , U and MAG/MSG extrapolation for  $0.35 \times 12~\mu\text{m}^2$  device, operating at  $V_{CB} = 0~V$

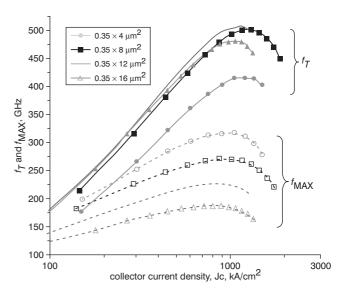

Fig. 3  $f_T$  and  $f_{MAX}$  against collector current density for multiple emitter length HBTs with 0.35  $\mu m$  emitter widths

Fig. 3 shows the cutoff frequency performance against collector current density for transistors with lengths of 4, 8, 12 and 16  $\mu$ m, each with an emitter junction width of 0.35  $\mu$ m. Peak performance was achieved at  $f_T$ = 509 GHz with a simultaneous  $f_{MAX}$  = 219 GHz at  $J_C$ =1150 kA/cm² for the 12  $\mu$ m device. The 0.35  $\times$  8  $\mu$ m² devices achieve  $f_T$ = 504 GHz with  $f_{MAX}$ = 261 GHz. These devices reach peak

$f_T$  at 36 mA, corresponding to a  $J_C = 1300 \, \mathrm{kA/cm^2}$ . For the  $0.35 \times 4 \, \mu \mathrm{m^2}$  devices,  $f_T$  and  $f_{\mathrm{MAX}}$  were 415 and 318 GHz, respectively. The reduction in  $f_T$  for the smaller device is attributed to an increase in emitter metal resistance. The observed increase in  $f_{\mathrm{MAX}}$  for the shorter emitter lengths is due to a decrease in base metal sheet resistance from transmission line effects as previously observed in [7].

Conclusion: InP/InGaAs SHBTs were fabricated to achieve cutoff frequencies greater than 500 GHz using a self-aligned submicron process. The thin collector structure allows a reduction of transit time, as well as an increase in peak current density due to an extension of  $J_{Kirk}$ . The performance of these transistors is suitable for future high-speed applications, with increasingly higher speed and lower power operation expected as further device scaling is exploited.

Acknowledgments: The authors wish to thank F. Strolli from BAE Systems for the DARPA-TFAST program management support, DARPA-TFAST program manager J.C. Zolper, and ARL contract manager A. Hung for program support.

© IEE 2003 8 August 2003 Electronics Letters Online No: 20030951 DOI: 10.1049/el:20030951

W. Hafez, Jie-Wei Lai and M. Feng (Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, 208 North Wright Street, Urbana, IL 61801, USA)

## References

- 1 IDA, M., KURISHIMA, K., and WATANABE, N.: 'Over 300 GHz  $f_T$  and  $f_{\rm MAX}$  InP/InGaAs double heterojunction bipolar transistors with a thin pseudomorphic base', *IEEE Electron Device Lett.*, 2002, **23**, pp. 694–696

- 2 HAFEZ, W., LAI, J.-W., and FENG, M.: 'Vertical scaling of 0.25 mm emitter InP/InGaAs single heterojunction bipolar transistors with  $f_T$  of 452 GHz', *IEEE Electron Device Lett.*, 2003

- 3 BOLOGNESI, C., DVORAK, M.W., MATINE, N., PITTS, O.J., and WATKINS, S.P.: 'Ultrahigh performance staggered lineup ('Type-II') InP/GaAsSb/InP NpN double heterojunction bipolar transistors', *Jpn. J. Appl. Phys*, 2002, **41**, pp. 1131–1135

- 4 SOKOLICH, M., S.T.III, and FIELDS, C.H.: 'High speed and low power InAlAs/InGaAs heterojunction bipolar transistors for dense ultra high speed digital applications'. Proc. 2001 IEEE Int. Electron Devices Mtg, 2001, Hong Kong, pp. 35.5.1–35.5.4

- 5 FUJIHARA, A., IKENAGA, Y., TAKAHASHI, H., KAWANAKA, M., and TANAKA, S.: 'High-speed InP/InGaAs DHBTs with ballistic collector launcher structure'. Proc. 2001 IEEE Electron Devices Mtg, 2001, Hong Kong, pp. 35.3.1–35.3.4

- 6 RIEH, J.-S., JAGANNATHAN, B., CHEN, H., SCHONENBERG, K., JENG, S.-J., KHATER, M., AHLGREN, D., FREEMAN, G., and SUBBANNA, S.: 'Performance and design considerations for high speed SiGe HBTs of  $f_T/f_{\rm max} = 375~{\rm GHz}/210~{\rm GHz}$ '. Int. Conf. on Indium Phosphide and Related Materials, Santa Barbara, CA, USA, 2003

- 7 HAFEZ, W., LAI, J.W., and FENG, M.: 'Record f<sub>T</sub> and f<sub>T</sub> + f<sub>max</sub> performance of InP/InGaAs single heterojunction bipolar transistors', *Electron. Lett.*, 2003, 39, (10), pp. 811–813

- 8 HATTENDORF, M.L., HARTMANN, Q.J., RICHARDS, K., and FENG, M.: 'Submicron scaling of high-speed InP/InGaAs SHBTs grown by MOCVD using carbon as the *p*-type dopant'. 2002 GaAs MANTECH Conf. Dig. Pprs, Scottsdale, AZ, USA, 2002, pp. 255–258