# Ultra High-Speed InP–InGaAs SHBTs With $f_{\text{max}}$ of 478 GHz

Daekyu Yu, Kyungho Lee, Bumman Kim, *Senior Member, IEEE*, D. Ontiveros, K. Vargason, J. M. Kuo, and Y. C. Kao, *Member, IEEE*

Abstract—InP-based single heterojunction bipolar transistors (SHBTs) for high-speed circuit applications were developed. Typical common emitter dc current gain  $(\beta)$  and BV $_{\rm CEO}$  were about 17 and 10 V, respectively. Maximum extrapolated  $f_{\rm max}$  of 478 GHz with  $f_T$  of 154 GHz was achieved for 0.5  $\times$  10  $\mu{\rm m}^2$  emitter size devices at 300 kA/cm $^2$  collector current density and 1.5 V collector bias. This is the highest  $f_{\rm max}$  ever reported for any nontransferred substrate HBTs, as far as the authors know. This paper highlights the optimized conventional process, and the authors have great hopes for the process that offers inherent advantages for the direct implementation to high-speed electronic circuit fabrication.

*Index Terms*—Base-collector capacitance, base resistance, heterojunction bipolar transistors (HBTs), high-speed devices.

## I. INTRODUCTION

NE OF the merits of InP-based HBTs is high speed and the HBTs have been used extensively for applications in fiber optical and wireless communication systems. We have developed the single HBT (SHBTs) for the purpose of high speed. Much effort has been made to reduce the base collector capacitance  $C_{\rm bc}$  and base resistance  $R_b$  of the HBT since  $f_{\rm max} \simeq \sqrt{f_T/8\pi R_b C_{\rm bc}}$ . Several process techniques to reduce  $R_b$  and  $C_{\rm bc}$ , such as isolation implantation of the extrinsic base and collector region [1], laterally etched undercut [2], epi regrowth for the thick base layer [3], L-shaped base electrode [4], horseshoe-shaped layout [5], and transferred-substrate technique [6] have contributed to a remarkable improvement in device performance.

However, this paper emphasizes the practical implementation of conventional processes. The base resistance  $(R_b)$  was minimized by optimizing the base contact resistivity. To reduce  $C_{\rm bc}$ , a base-pad-isolation structure was utilized, which can eliminate the capacitance at the base-pad area. Additionally, the emitter parasitic resistance and inductance were minimized by using emitter metal widening and air-bridge structures. These optimized conventional processes delivered extremely high-speed InP SHBTs.

Manuscript received February 3, 2003; revised March 20, 2003. This work was supported in part by the Agency for Defense Development, the BK-21 Project of the Ministry of Education, and the Ministry of Commerce, Industry and Energy. The review of this letter was arranged by Editor D. Ueda.

D. Yu, K. Lee, and B. Kim are with the Department of Electronic and Electrical Engineering and Microwave Application Research Center, Pohang University of Science and Technology (POSTECH), Pohang, Gyeongbuk 790-784, Korea (e-mail: sun13@postech.ac.kr).

D. Ontiveros, K. Vargason, J. M. Kuo, and Y. C. Kao are with Intelligent Epitaxy Technology (IntelliEPI), Inc., Richardson, TX 75081 USA.

Digital Object Identifier 10.1109/LED.2003.813367

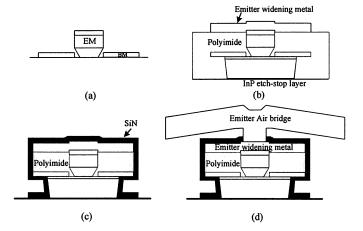

Fig. 1. Process flow (a) self-aligned base metal, (b) emitter metal widening, (c) SiN deposition, and (d) emitter air bridge.

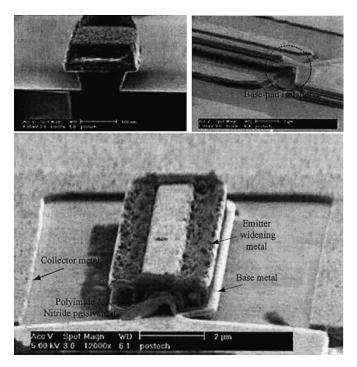

Fig. 2. SEM picture of the fabricated HBT with a 0.8 (effective 0.5)  $\times$  10  $\mu$  m<sup>2</sup> emitter area.

# II. DEVICE STRUCTURE AND FABRICATION

The epitaxial layer of the fabricated HBTs is grown by IntelliEPI using Solid Source Molecular Beam Epitaxy (SSMBE) on an Fe-doped semi-insulating (100) InP substrate. The

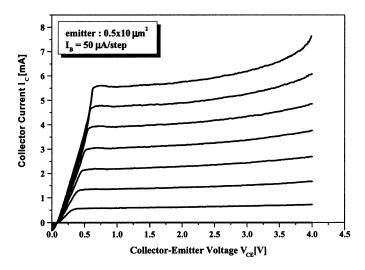

Fig. 3. Common emitter  $I_C$ – $V_{\rm CE}$  characteristics of the fabricated HBT with a 0.5  $\times$  10  $\mu$  m $^2$  emitter area.

layer structure includes, from the top, an InGaAs emitter contact layer, InGaAlAs graded layers, InP emitter (700 Å, Si-doped to  $7.0\times10^{17}~\rm cm^{-3}$ ), InGaAs base (400 Å, C-doped to  $6.0\times10^{19}~\rm cm^{-3}$  with 20 Å spacer), InGaAs collector layer (4000 Å, Si-doped to  $2.0\times10^{16}~\rm cm^{-3}$ ), and an InGaAs subcollector.

Fabrication started with the evaporation of the Ti-Pt-Au emitter contact metal having a width of 0.8  $\mu$ m. Emitter etch, which is one of the most delicate steps, was carried out by the selective etch of citric-based and subsequent hydrochloric-based wet processes, and the emitter was slightly undercut, resulting in an effective 0.5- $\mu$ m size. After the emitter etch, a self-aligned Pt-Ti-Pt-Au base metal with a width of 1  $\mu$ m was evaporated [Fig. 1(a)]. The emitter was protected by photo-resist using a base contact mask and the base and collector layers were then etched with a citric-based etchant. Next, Polyimide was coated and then flatly etched without a mask using an O<sub>2</sub> RIE until the emitter metal was exposed. Next, a Ti-Au emitter widening metal was evaporated [Fig. 1(b)], and second, the polyimide etch was performed until the epilayer was exposed. Next, SiN was deposited. The SiN was mask etched and the residual polyimide was removed by ashering [Fig. 1(c)] [7]. The subcollector was etched for device isolation. In this etching process, the active base area and the base pad area for interconnection were isolated. Next, Ti-Pt-Au collector metal and pad metal were evaporated. Lastly, Au air-bridge formation followed [Fig. 1(d)]. SEM pictures of the fabricated HBTs are shown in Fig. 2. For high-speed InP HBTs, the emitter and base metal widths were 0.8 (effectively  $0.5 \mu m$ ) and  $1 \mu m$ . The base-to-emitter spacing measured from the SEM picture was about 0.15  $\mu$ m.

## III. DEVICE MEASUREMENT RESULTS

I-V curves of the fabricated HBTs with  $0.5 \times 10~\mu\text{m}^2$  emitter area are measured and are depicted in Fig. 3. As shown, the common-emitter dc current gain  $(\beta)$  of the fabricated HBTs is about 17 at a collector current density of  $1 \times 10^5~\text{A/cm}^2$ . Breakdown voltages of the fabricated HBTs at an open base,  $BV_{CEO}$  is very high, about 10 V. Base sheet resistance  $(R_{SB})$  of 560  $\Omega/\square$  and specific contact resistivity  $(\rho_{BC})$  of

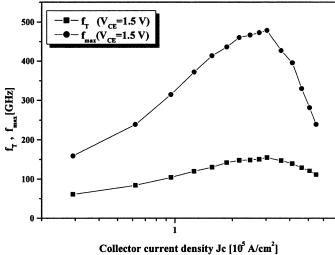

Fig. 4. Dependence of  $f_T$  and  $f_{\rm max}$  on collector current density of the fabricated HBT with a  $0.5 \times 10~\mu{\rm m}^2$  emitter area.

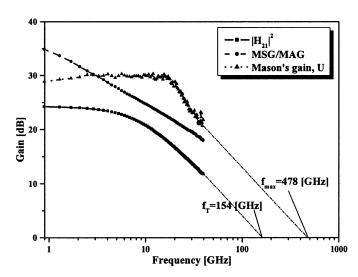

Fig. 5. Frequency dependencies of  $|h_{21}|^2, {\sf MSG/MAG},$  and Mason's gain (no pad-deembedding).

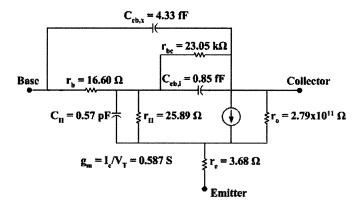

Fig. 6. Small-signal equivalent circuit model at  $I_C=15.2~\mathrm{mA}$  and  $V_{\mathrm{CE}}=1.5~\mathrm{V}.$

$2.5 \times 10^{-7}~\Omega\cdot\mathrm{cm}^2$  are measured using Transmission Line Measurement (TLM). The transfer length  $L_T$ , expressed as  $(\rho_{\mathrm{BC}}/R_{\mathrm{SB}})^{1/2}$ , is 0.21  $\mu\mathrm{m}$  and the base contact resistance is maintained low.

The microwave performance of the fabricated HBTs is characterized by on-wafer S-parameter measurements from 0.5 to 40 GHz using a Agilent 8510C network analyzer calibrated by thru-reflect-line (TRL) method.  $f_T$  and  $f_{\rm max}$  are estimated assuming a -20 dB/decade frequency dependence of the current gain and Mason's unilateral gain, respectively. Fig. 4 shows the dependence of  $f_T$  and  $f_{\rm max}$  on collector current density at 1.5 V collector bias. Frequency dependencies of the current gain, Mason's unilateral gain, and maximum stable gain/maximum available gain are shown in Fig. 5.  $f_T$  and  $f_{\rm max}$  of the HBT are 154 and 478 GHz (Gain  $\simeq 21.7$  dB at 40 GHz), respectively, at  $I_C=15.2$  mA and  $V_{\rm CE}=1.5$  V. To our knowledge, this is the highest  $f_{\rm max}$  ever reported for any nontransferred substrate HBTs.

From the measured S-parameters, small-signal model parameters of the device are extracted and are shown in Fig. 6. Despite the conventional structure, the time constant  $R_bC_{\mathrm{bc},i}$  is evaluated to be very low, about 14.11 fs. This is due to the low base contact resistance, since the transfer length  $(L_T)$ , expressed as  $(\rho_{\mathrm{BC}}/R_{\mathrm{SB}})^{1/2}$  ( $\simeq$ 0.21  $\mu$ m), remains shorter than the effective base width ( $\simeq$ 1  $\mu$ m), although the base layer is attacked during the base and collector layer etchings. Also, the extrinsic base collector capacitance  $(C_{\mathrm{cb},x})$  is very low, 4.33 fF, since the base-pad is isolated. The emitter resistance  $(r_e)$  is maintained low by using the emitter metal widening and air-bridge structures even though the emitter width is small, about 0.5  $\mu$ m. These improved structure results in the very high-speed HBT.

## IV. CONCLUSION

High-speed InP-InGaAs SHBTs are fabricated by using the POSTECH process. The processes include good base ohmic contact, base-pad isolation, emitter metal widening, and air-bridge structures. High-frequency performance of  $f_T=154~{\rm GHz}$  and  $f_{\rm max}=478~{\rm GHz}$  is obtained from the HBT with a  $0.5\times 10~\mu{\rm m}^2$  emitter area. This is the highest  $f_{\rm max}$  ever reported for any nontransferred substrate HBTs. This conventional process can be a practical technique for implementation to high-speed electronic circuits. Also, as the device is scaled down, the device RF performance will be further improved.

#### ACKNOWLEDGMENT

#### REFERENCES

- O. Nakajima, K. Nagata, Y. Yamaguchi, H. Ito, and T. Ishibashi, "Improvement in AlGaAs/GaAs HBT power gains with buried protonimplanted layer," *Electron. Lett.*, vol. 22, no. 25, pp. 1317–1318, 1986.

- [2] W. Liu, D. Hill, H. Chau, J. Sweder, T. Nagle, and J. Delaney, "Laterally etched undercut (LEU) technique to reduce base-collector capacitances in heterojunction bipolar transistors," in *IEEE GaAs IC Symp. Dig.*, 1995, pp. 167–170.

- [3] H. Shimawaki, Y. Amamiya, N. Furuhata, and K. Honjo, "High- $f_{\rm max}$  AlGaAs/InGaAs and AlGaAs/GaAs HBT's with p+/p regrown base contacts," *IEEE Trans. Electron Devices*, vol. 42, pp. 1735–1744, Oct. 1905

- [4] M. Yanagihara, H. Sakai, Y. Ota, M. Tanabe, K. Inoue, and A. Tamura, "253-GHz f<sub>max</sub> AlGaAs/GaAs HBT with Ni/Ti/Pt/Ti/Pt-contact and L-Shaped base electrode," in *IEDM Tech. Dig.*, 1990, pp. 807–810.

- [5] W. Kim, K. Lee, M. Chung, J. Kang, and B. Kim, "High-speed Al-GaAs/GaAs HBT's with reduced base-collector capacitance," *Electron. Lett.*, vol. 37, no. 20, pp. 1259–1261, Sept. 2001.

- [6] M. Rodwell, Y. Betser, S. Jaganathan, T. Mathew, P. K. Sundararajan, S. C. Martin, R. P. Smith, Y. Wei, M. Urteaga, D. Scott, and S. Long, "Submicron lateral scaling of HBT's and other vertical-transport devices: Toward THz bandwidths," in *GaAs 2000 Conf. Proc.*, Paris, France, Oct. 2000, pp. 1–4.

- [7] K. Lee, D. Yu, M. Chung, J. Kang, and B. Kim, "New collector undercut technique using a SiN sidewall for low base contact resistance in InP/In-GaAs SHBTs," *IEEE Trans. Electron Devices*, vol. 49, pp. 1079–1082, June 2002.