# Submicron InP–InGaAs Single Heterojunction Bipolar Transistors With $f_T$ of 377 GHz

Walid Hafez, Jie-Wei Lai, and Milton Feng, Fellow, IEEE

Abstract—Submicron InP–InGaAs-based single heterojunction bipolar transistors (SHBTs) are fabricated to achieve record-breaking speed performance using an aggressively scaled epitaxial structure coupled with a submicron emitter process. SHBTs with dimensions of 0.35  $\times 16~\mu m$  have demonstrated a maximum current gain cutoff frequency  $f_T$  of 377 GHz with a simultaneous maximum power gain cutoff frequency  $f_{\rm MAX}$  of 230 GHz at the current density Jc of 650 kA/cm². Typical  $\rm BV_{CEO}$  values exceed 3.7 V.

Index Terms—Heterojunction bipolar transistors (HBTs).

#### I. INTRODUCTION

THE high-frequency performance of InP-based heterojunction bipolar transistors (HBTs) has steadily increased over the last few years. While double heterojunction transistors (DHBTs) have received much attention recently, InGaAs-based DHBT devices require complicated grading schemes to overcome current blocking at the base-collector junction [1]–[4], and high-quality GaAsSb material [5] is still difficult to obtain. In this paper, we report the fastest bipolar transistor to date using a simplistic SHBT layer structure. The submicron emitter dimensions allow for low-power operation while maintaining excellent dc characteristics. Such devices are critical to support high-speed low-power applications, such as 40-Gb/s OEIC receivers [6], [7] and analog-to-digital converters.

#### II. LAYER STRUCTURE

The epitaxial structure used in this work was directed toward achieving high current cutoff frequencies  $(f_T)$  by scaling the layer thicknesses and high-power cutoff frequencies  $(f_{\rm MAX})$  by a submicron lateral scaling process. The wafers were grown on Fe-doped semi-insulating (100) InP substrates by MBE. The layer structure is scaled from the previously reported University of Illinois at Urbana–Champaign (UIUC) structure in [6], [8]. The emitter doping level is increased to reduce emitter parasitic resistances and enhance current injection efficiency. The structure also employs a 300-Å compositionally graded base with an Indium mole fraction of 0.5 to 0.53 and C-doped  $(p=5\times10^{19}~{\rm cm^{-3}},R_{\rm sb}=970~\Omega/{\rm sq})$  grown on a 1500-Å InGaAs collector. The design of the material structure has been specialized for UIUC submicron processing.

Manuscript received January 20, 2003; revised February 26, 2003. The review of this letter was arranged by Editor D. Ueda.

The authors are with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL 61801 USA.

Digital Object Identifier 10.1109/LED.2003.812530

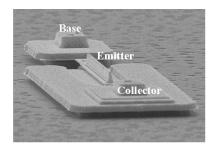

Fig. 1. Fabricated 0.35- $\mu$ m  $\times$  8  $\mu$ m InP–InGaAs SHBT before planarization.

### III. FABRICATION

The high-frequency devices were fabricated using a standard mesa process, utilizing both electron-beam and optical contact lithography. The process features an airbridge (referred to as a  $\mu$  bridge in this work) to isolate the base terminal from the active device, thereby drastically reducing extrinsic parasitic capacitances. The fabrication relies exclusively on wet etching to achieve the undercutting desired to allow both the self-aligned base metal and the  $\mu$ -bridge release.

Hexagonal emitters were defined using a Leica/Cambridge EBMF 10.5 e-beam system, resulting in a minimum emitter footprint of 0.35  $\mu$ m. The undercut during the emitter-base etch was precisely controlled to within 60 nm. The self-aligned base metal pattern was also e-beam defined, and a 650-Å Ti-Pt-Au base metal stack was then deposited by e-beam evaporation. The use of such thin base metal did not adversely affect the mechanical robustness of the  $\mu$  bridge. The devices are electrically isolated while simultaneously releasing the  $\mu$  bridge and then planarized and encapsulated with bizbenzocyclobutene (BCB). The cured BCB provides structural support to the  $\mu$  bridge during subsequent high-temperature processing steps. An etchback using a reactive ion etch (RIE) is then performed to expose the base, emitter, and collector terminals. NiCr resistors for on-wafer calibration are thermally deposited, followed by e-beam deposition of the overlay RF pads. An SEM image of a fabricated  $0.35 \times 8 \mu m$  device before planarization is shown in Fig. 1.

#### IV. DC RESULTS

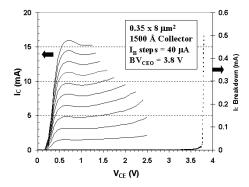

Typical values of dc gain vary from 25 to 40 between 1  $\mu$ A and 1 mA, with  $\beta$  remaining constant at 40 above 1 mA. Base and collector ideality factors are 1.35 and 1.18, respectively. A common emitter family of curves is shown in Fig. 2, where the collector–emitter offset voltage  $V_{\rm CE, offset}$  is approximately 0.17 V and the knee voltage is less than 0.7 V. The commonemitter breakdown voltage  $BV_{\rm CEO}$  is approximately 3.8 V for

Fig. 2. Family of curve plots for a  $0.35 \times 8 \mu m$  device.

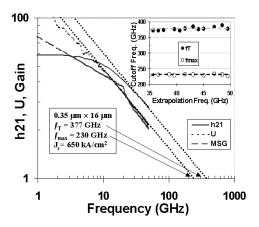

Fig. 3. Extrapolation of  $h_{21}$ , U, and MSG and  $f_T$ ,  $f_{\rm MAX}$  versus extrapolation frequency.

the  $0.35 \times 8~\mu\mathrm{m}^2$  device, and the avalanche breakdown at the peak  $f_T$  collector current is 2 V.

## V. RF RESULTS

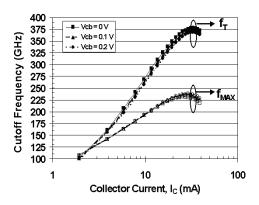

The HBTs were characterized with an HP8510C network analyzer from 0.5 to 50 GHz. The calibration was performed with on-wafer short-open-load-thru (SOLT) standards. The current gain, Mason's unilateral gain, and MSG/MAG for a  $0.35 \times 16 \ \mu m^2$  HBT are shown in Fig. 3. The cutoff values were obtained by averaging the -20 dB/decade extrapolations from 35 to 50 GHz. The dependence of  $f_T$  and  $f_{\rm MAX}$  versus extrapolation frequency is shown in the inset of Fig. 3. The peak RF performance yields an  $f_T$  of 377 GHz and occurs at an Ic of 31 mA, corresponding to a Jc of 650 kA/cm<sup>2</sup> when device undercutting is factored into the emitter area calculation. An  $f_{\rm MAX}$  of 230 GHz was achieved simultaneously at a  $V_{\rm CB}$ of 0 V. Fig. 4 shows the cutoff frequencies versus collector current for various  $V_{\rm CB}$  voltages. At  $V_{\rm CB}$  of 0.1 V, the peak values for  $f_T$  and  $f_{MAX}$  are 368 and 238 GHz respectively, showing a weak dependence of the collector-base voltage on RF performance. We have also measured several HBTs with different emitter length as shown in Table I. For a  $0.35 \times 8 \mu m^2$ HBT, an  $f_T$  of 370 GHz with associated  $f_{MAX}$  of 280 GHz was achieved. An alternative layout for the  $0.35 \times 8 \ \mu m^2$ HBT, featuring a narrower base metal finger, yielded an  $f_T$  of 363 GHz with associated  $f_{\rm MAX}$  of 310 GHz.

Fig. 4.  $f_T$  and  $f_{MAX}$  and versus collector current for various  $V_{CB}$  voltages.

TABLE I

PERFORMANCE SUMMARY FOR CURRENT BIPOLAR TECHNOLOGIES

| Source          | $f_{r}$ (GHz) | f <sub>max</sub><br>(GHz) | J <sub>C</sub><br>(kA/cm²) | β    | $W_{\underline{s}} \times L_{\underline{s}}$ $(\mu m^2)$ | <i>BV<sub>c∎0</sub></i><br>(V) |

|-----------------|---------------|---------------------------|----------------------------|------|----------------------------------------------------------|--------------------------------|

| HRL InP SHBT    | 180           | 220                       | 250                        | 30   | 0.5 x 4                                                  | 2                              |

| SFU In P DHBT   | 300           | 300                       | 410                        | 45   | 0.4 x 11                                                 | 6                              |

| NTT InP DHBT    | 341           | 238                       | 833                        | 34   | 0.8 x 3                                                  | 2                              |

| IBM SiGe 9HP    | 350           | 170                       | 2000                       | 2300 | 0.12 x 2.5                                               | 1.4                            |

| UIUC InP SHBT-1 | 363           | 310                       | 667                        | 40   | 0.35 x 8                                                 | 3.7                            |

| UIUC InP SHBT-2 | 370           | 280                       | 683                        | 40   | 0.35 x 8                                                 | 3.8                            |

| UIUC InP SHBT-3 | 377           | 230                       | 650                        | 40   | 0.35 x 16                                                | 4.1                            |

|                 |               |                           |                            |      |                                                          |                                |

A summary of the characteristics of the most recent high-speed bipolar transistor is shown in Table I. The  $f_T*\mathrm{BV}_{\mathrm{CEO}}$  product for the UIUC devices exceeds 1550 GHz  $\cdot$  V, well above the Johnson limit of 200 GHz  $\cdot$  V [9]. In comparison, the UIUC InP–InGaAs SHBT surpass the best reported SiGe HBT (490 GHz  $\cdot$  V) [10], InAlAs–InGaAs SHBT (360 GHz  $\cdot$  V) [11] and InP–InGaAs DHBT(682 GHz  $\cdot$  V) [1] and approach the latest InP–GaAsSb DHBT (1800 GHz  $\cdot$  V) [5].

Transistor model parameter extraction was performed to better understand the dominant delay terms limiting the device speed. The major delay terms are as follows:  $\tau_F=0.35$  ps, (kT/Ic)Cje = 0.056 ps, (kT/Ic)C<sub>BC</sub> = 0.023 ps,  $R_EC_{\rm BC}=0.027$  ps and  $R_BC_{\rm BC}=0.20$  ps. These equivalent circuit parameters confirm the dominant delays are due to the forward transit time,  $\tau_F$ , and the base-collector charging capacitance,  $R_BC_{\rm BC}$ .

# VI. CONCLUSION

This paper has demonstrated superior dc and RF characteristics for SHBTs. The aggressive scaling of the epitaxial structure coupled with submicron emitter dimensions has produced record current gain cutoff frequencies. The RF performance along with the high-breakdown voltages exceeding 3.7 V suggest that SHBT devices will be important for low-voltage low-power mixed signal circuit applications.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. M. Hattendorf (Intel), Dr. D. Caruth (Xindium Technology, Inc.), and Dr. S. C. Shen (Xindium Technology, Inc.) for helpful discussions in process development, material, and measurement support. The authors would also like to thank Mr. F. Strolli from BAE System for the DARPA-TFAST program management support. The authors would also like to thank DARPA-TFAST program manager Dr. J. Zolper and ARL contract manager A. Hung for program support.

#### REFERENCES

- [1] M. Ida, K. Kurishima, N. Watanabe, and T. Enoki, "InP/InGaAs DHBT's with 341 GHz fT at high current density of over 800 kA/cm<sup>2</sup>," presented at the IEDM, Washington, DC, pp. 35.4.1–35.4.4.

- [2] R. Malik, R. A. Hamm, R. F. Kopf, R. W. Ryan, R. K. Montgomery, J. Lin, D. A. Humphrey, A. Tate, and Y. K. Chen, "Self-aligned thin emitter C-doped base InP/InGaAs/InP DHBT's for high speed digital and microwave IC applications," in 54th Annu. Device Research Conf. Dig., 1996, pp. 40–41.

- [3] D. Sawadi, E. Kaneshiro, A. Gutierrez-Aitken, P. C. Grossman, K. Sato, W. Kim, G. Leslie, J. Eldredge, T. Block, P. Chin, L. Tran, A. K. Oki, and D. C. Streit, "High performance, high yield InP DHBT production process for 40 Gbps applications," in *Proc. 2001 IEEE Int. Conf. Indium Phosphide and Related Materials*, May 2001, pp. 493–496.

- [4] A. Fujihara, Y. Ikenaga, H. Takahashi, M. Kawanaka, and S. Tanaka, "High-speed InP/InGaAs DHBT's with ballistic collector launcher structure," presented at the IEDM, Washington, DC, pp. 35.3.1–35.3.4.

- [5] C. Bolognesi, M. W. Dvorak, N. Matine, O. J. Pitts, and S. P. Watkins, "Ultrahigh performance staggered lineup ("Type-II") InP/GaAsSb/InP NpN double heterojunction bipolar transistors," *Jpn. J. Appl. Phys.*, pt. 1, vol. 41, no. 2B, pp. 1131–1135, Feb. 2002.

- [6] S. C. Shen, D. C. Caruth, and M. Feng, "Performance of InP/InGaAs heterojunction bipolar transistors for 40 Gb/s OEIC applications," in 2002 GaAs MANTECH Conf. Dig., Apr. 2002, pp. 22–25.

- [7] D. Caruth, S. C. Shen, D. Chan, M. Feng, and J. Schutt-Aine, "A 40 Gb/s integrated differential PIN + TIA with dc offset control using InP SHBT technology," in 2002 GaAs IC 24th Annu. Tech. Dig., Oct. 2002, pp. 59–62.

- [8] M. L. Hattendorf, Q. J. Hartmann, K. Richards, and M. Feng, "Sub-micron scaling of high-speed InP/InGaAs SHBT's grown by MOCVD using carbon as the p-type dopant," in 2002 GaAs MANTECH Conf. Dig., Apr. 2002, pp. 255–258.

- [9] E. O. Johnson, "Physical limitations on frequency and power parameters of transistors," RCA Rev., vol. 26, pp. 163–177, June 1965.

- [10] J. S. Rieh, B. Jagannathan, H. Chen, K. T. Schonenberg, D. Angell, A. Chinthakindi, J. Florkey, F. Golan, D. Greenberg, S.-J. Jeng, M. Khater, F. Pagette, C. Schnabel, P. Smith, A. Stricker, K. Vaed, R. Volant, D. Ahlgren, G. Freeman, K. Stein, and S. Subbanna, "SiGe HBT's with cut-off frequency of 350 GHz," in *IEDM Tech. Dig.*, Dec. 2002, pp. 771–774.

- [11] M. Sokolich, S. Thomas, III, and C. H. Fields, "High speed and low power InAlAs/InGaAs heterojunction bipolar transistors for dense ultra high speed digital applications," in *IEDM*, Washington, DC, pp. 35.5 1–35.5.4